SemiWiki: A Last-Level Cache for SoCs

by On Jul 26, 2018

A Last-Level Cache for SoCs

July 19th, 2018 – By Bernard Murphy

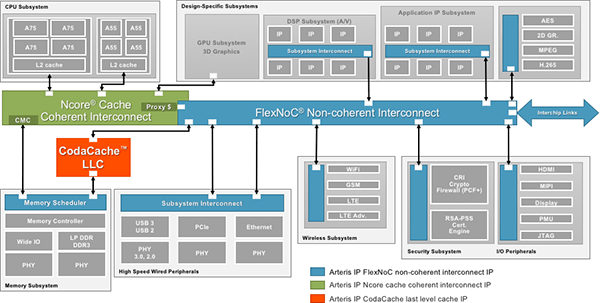

Based on a discussion with JP Loison, Bernard Murphy (SemiWiki) describes Arteris IP’s latest IP introduction – a last-level cache (LLC) for use outside the coherent domain, for accelerators and other IP that can benefit from cache support. He also touches on benefits offered by significant flexibility in adapting the IP for different use-models.

Based on a discussion with JP Loison, Bernard Murphy (SemiWiki) describes Arteris IP’s latest IP introduction – a last-level cache (LLC) for use outside the coherent domain, for accelerators and other IP that can benefit from cache support. He also touches on benefits offered by significant flexibility in adapting the IP for different use-models.

We tend to think of cache primarily as an adjunct to processors to improve performance. Reading and writing main memory (DRAM) is very slow thanks to all the package and board impedance between chips. If you can fetch blocks of contiguous memory from the DRAM to a local on-chip memory, locality of reference in most code ensures much faster access for many subsequent operations which will frequently find the data/addresses they need in these cached copies. This greatly improves overall performance, despite need at times to update cache contents from a different location (and maybe store back in DRAM what must be evicted from the cache).

To read the entire article, please click here:

https://www.semiwiki.com/forum/content/7605-last-level-cache-socs.html