# ARTERS IP

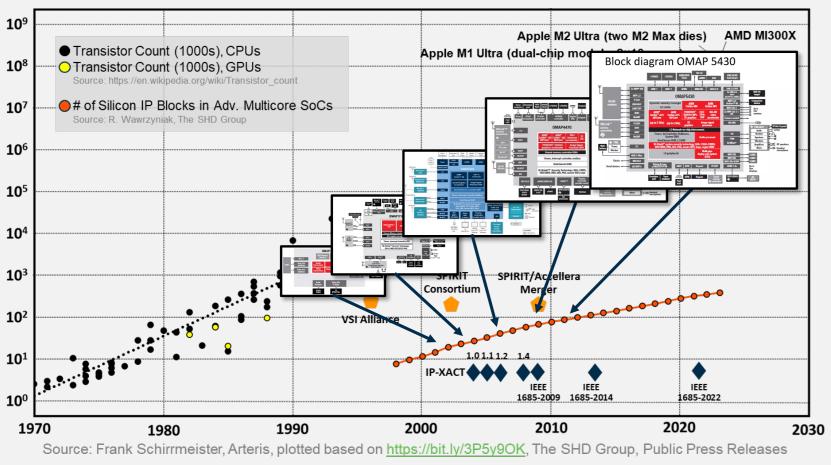

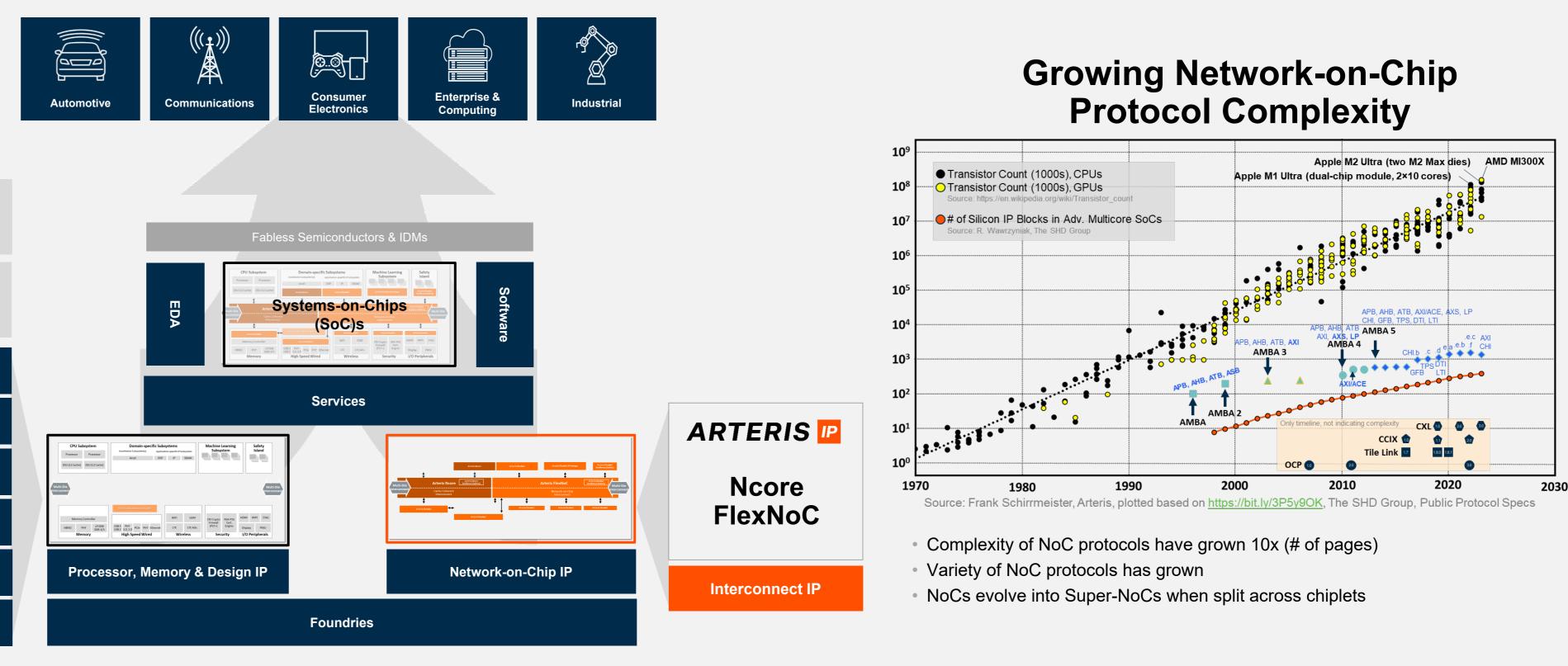

#### **Growing SoC Integration Complexity # of IP blocks, IP-XACT**

- # of IP Blocks in SoC has grown from 10s to 100s

- Disaggregation offers design version variety

- Standards like IP-XACT need to extend too

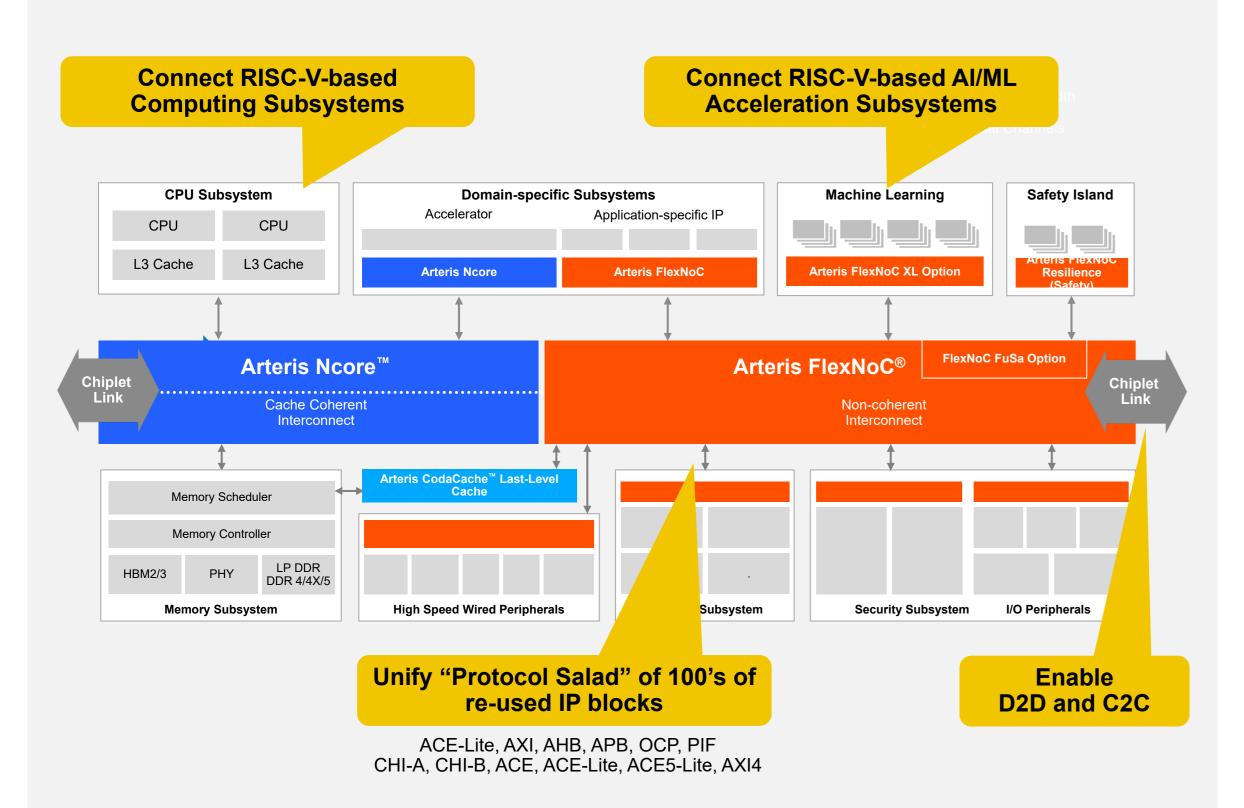

### **De-risk RISC-V SoC Integration**

## Enabling the RISC-V and Chiplet Era Through **Accelerated Network-on-Chip (NoC) Development**

Frank Schirrmeister, Guillaume Boillet

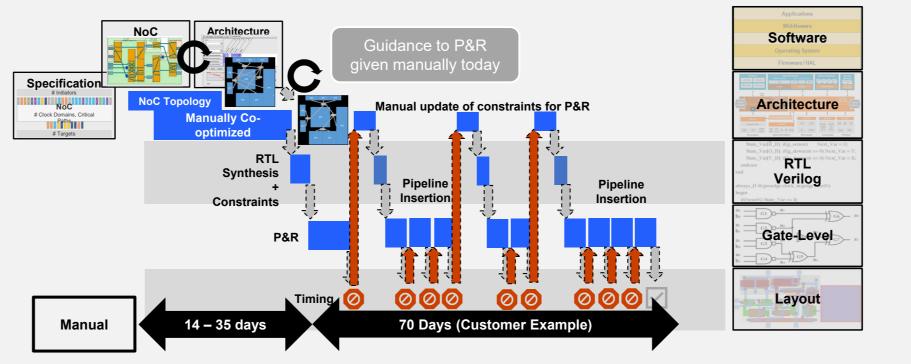

#### Manual Flow With Some Layout **Awareness & Guidance**

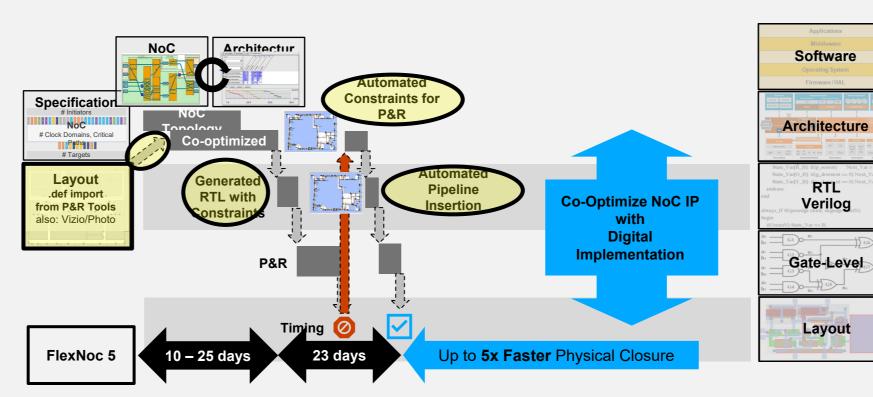

#### The Solution: FlexNoC 5 Physically Aware NoC IP with Pipeline Optimization

**66** We are happy to share that we are partnering with Arteris to use Ncore and *FlexNoC IP in our next-generation product, The combination of performance* and features made it a great choice for both our AI chips and our highperformance RISC-V CPUs. The Arteris team and IP solved our on-chip network problems so we can focus on building our next-generation AI and RISC-V CPU products."

୍ୟା Chiplets

#### **Arteris FlexNoC 5 Physically Aware Network-on-Chip IP**

- Up to 5X faster physical closure over manual iterations • Early physical awareness for faster convergence without re-designs

- Allows place and route tools a better starting point • Shrinks interconnect area by 15% or more (vs pipeline over-

- provisioning)

- Reduces NoC IP power due to less pipeline logic and fewer LVT cells **Engineering efficiency**

- · Reducing hours of work to minutes, removing iteration loops

- Automated NoC element preparation for the timing closure process • Seamless integration of GUI windows for new physically aware flow · Topology visualized directly on floorplan with user-selectable filter options

- Other enhancements

- Automates import/export of NoC configurations with Arteris Magillem • Debug and Trace with ATB 128b and timestamps support

- AMBA 5 support of DVM 8.1 (Device Virtual Messaging)

- Re-order Buffer Optimization benefitting Cache and DRAM connectivity

**Enables SoC developers to build NoCs with faster physical closure!**

tenstorrent ARTERIS Tenstorrent Selects Arteris IP for Al High-Performance Computing and Datacenter RISC-V