Simulation and Modeling with Arteris FlexExplorer

Cut turn-around time and shrink schedules with automatically generated Accellera SystemC TLM 2.x models of your specific interconnect configuration.

Arteris FlexNoC Interconnect SystemC TLM models are automatically generated based on the end-user’s specific interconnect configuration. The models are used within FlexNoC’s FlexExplorer module for quick turn-around script- and scenario-based performance evaluation and have associated Accelera IP-XACT descriptions.

These models can also be exported from FlexNoC for easy import into system-level modeling tool suites like Synopsys Platform Architect, and are created at 3 levels of abstraction.

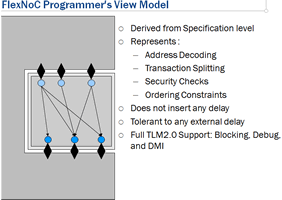

Programmer’s View Models

TLM 2.x LT Loosely-Timed

FlexNoC Programmer’s View models are derived from the interconnect’s Specification level and represent Address Decoding, Transaction Splitting, Security Checks, Ordering Constraints. They have full TLM 2.x LT support for blocking, debug, and direct memory interface (DMI).

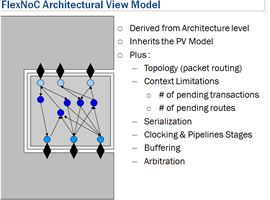

Architectural View Models

TLM 2.x Approximately-Timed

FlexNoC Architectural View models are derived from the interconnect’s Architecture level, inheriting aspects of the PV model while also representing Topology (packet routing), Context Limitations (# of pending transactions, # of pending routes), Serialization, Clocking & Pipelines Stages, Buffering and Arbitration.

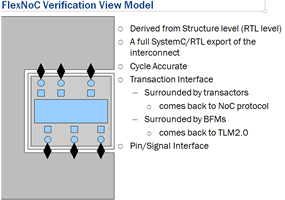

Verification View Models

TLM 2.x CA Cycle-Accurate

FlexNoC Verification View models are derived from the interconnect’s Structure/RTL level. They are TLM 2.x Cycle-Accurate and can have a transactor/bus functional model (BFM) interface or a pin/signal interface.

Using the built-in FlexExplorer simulation capabilities, we were able to try many candidate architectures and configurations in very short turn-around-times. This enabled us to quickly optimize our SoC by implementing FlexNoC’s many advanced features. We were able to meet all functional, performance, area and frequency requirements without suffering any backend layout or timing issues. Using FlexNoC IP was key to our team’s success.

Yasunori Maki, Senior Manager, Lifestyle Solutions Development Center, Toshiba Corporation