Ease (& Automate) timing closure

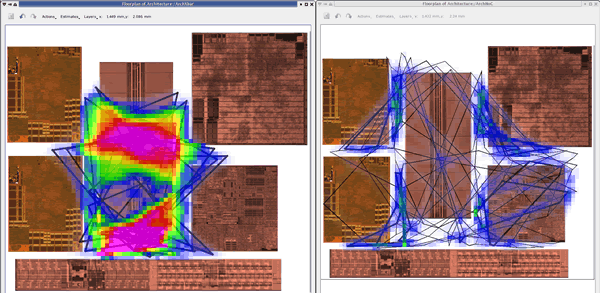

Arteris NoC technology reduces or eliminates wire routing congestion, which helps avoid timing closure issues in the backend. With our new flagship FlexNoC Physical IP, users can now visualize and proactively address any remaining issues early in the design cycle.

|

| The traditional OCP crossbar on the left has pronounced routing congestion. The same IP with fewer wires due to use of Arteris FlexNoC interconnect IP has no routing congestion. The protocols are OCP for both. Source: Arteris customer design. |

Wire routing congestion creates timing closure issues

Routing congestion makes timing closure (also known as “timing convergence”) more difficult because as the less resistive upper metal layers are quickly consumed, the EDA routing tools attempt to route long or timing-critical paths on more resistive middle and lower metal layers. The decreased cross-sectional area of the wires in the middle and lower metal layers leads to increased resistance which causes greater wire delays over longer distances.

Furthermore, as resistance in wires increases, timing closure and timing convergence issues caused by wire delays, Vdroop, poor clock skew/slew and delays in global clock distribution become more likely.

Average distances become longer because as g-cells become unavailable due to routing congestion, the EDA tools will route wires around these congested areas, increasing wire length and adding signal delay proportional to the increase in length of the wire. These signal delays contribute to the time it takes to achieve timing closure.

Timing closure = failure to meet design frequencies + missed schedules

When target frequencies cannot be met due to timing closure issues on a certain path, the back-end designer will add repeater registers that store and hold a data value for a clock cycle, forming a multi-cycle pipelined data flow. These pipeline registers consume power and area.

Finding the root cause of timing issues, determining the solution, then implementing it used to take days and sometimes weeks. We are now able to solve these issues in hours. This huge reduction in troubleshooting and problem resolution time frees us up to work on other aspects of the SoC.

Netanel Zeevi, ASIC Engineer, Mobileye