Packetization & Serialization

The term “NoC” is often thrown around loosely in industry and academia. The key requirements for any NoC are the data must be transformed into data packets and these packets can be sized to be sent (or serialized) in many bit-widths.

Packetization

With Arteris NoC technology, network interface units (NIU) manage communication with a connected IP core. NIUs convert traditional AMBA, OCP and proprietary protocol load and store transactions into packets for transport across the network.

At the periphery of the network, NIUs communicate with the attached IP cores via one of a number of standard IP sockets (interfaces), or through custom-built sockets developed by Arteris to meet specific customer needs.

Serialization

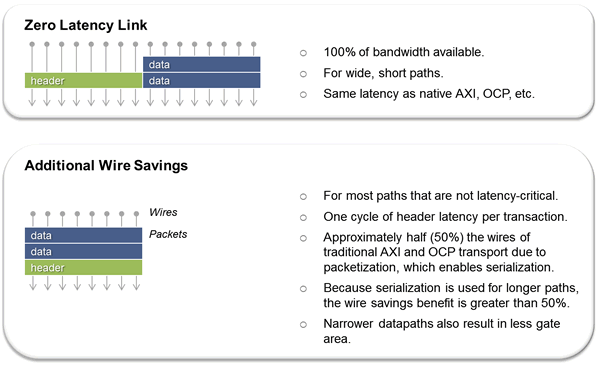

Compared to other interconnects, Arteris technology requires fewer connections and wires, provides fully pipelinable units, and simplifies timing closure.

The physical layer defines how packets are actually transmitted between NoC units. Various link types with different capabilities, such as transport links, globally asynchronous / locally synchronous (GALS) links for longer distances, or Chip-to-Chip links, can be employed.

Separate transaction and transport layers make it possible to change links, or their characteristics, without affecting the transport or transaction layers. Because all connections are point-to-point, high-fanout nets are prevented, thus providing better performance and easier routing.

Because most of the interconnect logic is resident in NIUs that are close to their respective IP blocks, there are fewer gates to place for the interconnect itself.

The Arteris interconnect IP offers us a convenient solution to handle the high speed communication needed between our SoC and external modem IC. Our customers will benefit from the lower BOM cost and power consumption as a result of this IP. We look forward to Arteris’ interconnect IP helping us shorten development schedules and lower risks associated with compatibility.

Thomas Kim, Vice President, SoC Platform Development, System LSI, Samsung Electronics