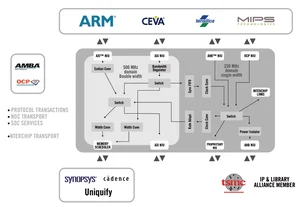

Clock, voltage and frequency domains

Today’s SoCs require advanced power management capabilities like dynamic voltage and frequency scaling (DVFS) to be competitive in power consumption and heat dissipation. Arteris NoC technology and graphical tools makes it easy to define and verify any number of independent clock, voltage and power domains in the interconnect to easily create complex power management schemes.

Today’s SoCs require advanced power management capabilities like dynamic voltage and frequency scaling (DVFS) to be competitive in power consumption and heat dissipation. Arteris NoC technology and graphical tools makes it easy to define and verify any number of independent clock, voltage and power domains in the interconnect to easily create complex power management schemes.

Clock gating

Dynamic Clock Gating is used so interconnect resources are only clocked when processing packets.

A versatile clock manager supports any clock and reset policy. Power domain partitioning is supported by power controller, power disconnect, and error handling IP within the interconnect. And voltage domains are automatically accommodated by automatically inserted asynchronous crossings and level shifter cells.

GALS (globally asynchronous/locally synchronous)

GALS technology is used for maximum clock domain management efficiency. Cross-clock boundaries are instantiated using small unidirectional bi-synchronous FIFOs, allowing for optimal latency with no handshake required. Clock boundaries can be partitioned along any link within the interconnect and the GALS elements can be bypassed for synchronous operation.

Power and voltage domains are separated by an electrical isolation layer, and individual IP blocks can be turned off using socket disconnect protocols. Retention registers are inserted when specific IP blocks must retain state when the power domain is shut off.

Power intent (CPF and UPF)

Power intent is captured and exported using the Common Power Format (CPF) and the Unified Power Format (UPF).

Our successful adoption of Arteris FlexNoC fabric IP has been straightforward, allowing us to more quickly architect and implement sophisticated systems-on-chip in less time and with better power consumption and performance.

Fares Bagh, Vice President of R&D, Freescale