Boost safety & SSD endurance with FlexNoC FuSa hardware-centric solution meeting ISO 26262 & IEC 61508. Ideal for automotive & enterprise, ECC, built-in self-tests. Mobileye, SemiDrive, & Intel.

Enabling Safety & Reliability for Automotive and Enterprise Computing

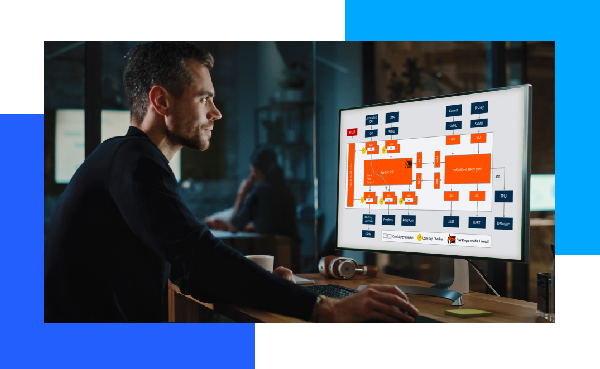

The world’s #1 on-chip fabric is used by the world’s top semiconductor design teams as the backbone on-chip communications for chips targeting the fastest growing markets.

The latest generation FlexNoC 5 Interconnect with its integrated physical awareness technology, gives place and route teams a much better starting point while simultaneously reducing interconnect area and power consumption. FlexNoC 5 delivers up to 5X shorter turn-around-time versus manual physical iterations.

ISO 26262 Certifiable for Automotive Safety and Reliability for Industrial and Enterprise Endurance.

Download Reliability (Industrial) Datasheet

Download Reliability (Enterprise) Datasheet

Next-Gen Protection: From Core Safety to Data Integrity

Boosted safety & compliance, efficient hardware focus, thorough data protection

Enhanced Safety and Reliability

Integrate hardware reliability and functional safety features, ensuring compliance with ISO 26262 and IEC 61508, crucial for sectors like automotive and enterprise computing SSD endurance.

Hardware-Centric Approach

FlexNoC drives performant on-chip data flow and access to off-chip memory by enabling multi-channel HBM2 memory and high bandwidth data paths.

Comprehensive Data Protection

Ensure data traffic protection throughout the chip floorplan with error-correcting code (ECC), support for ARM Cortex processors, built-in self-tests, and unit redundancy.

Safety and Reliability Options Key Features

- ECC Interface & Transport: Detects/corrects errors for data integrity.

- Packet Consistency Checkers: Verifies data packet consistency in transmission.

- Unit Duplication: Enables fault detection via SoC design redundancy.

- Initiator Timeout: Detects non-responsive initiators, preventing failures.

- FMEDA Generation: Analyzes failure modes & implements countermeasures.

- Fault Reporting BIST: Detects system faults for accurate issue identification

- Easy partitioning of any SoC into safe and non-safe domain

Safety and Reliability Options Product Benefits

Comprehensive Standards Compliance

Meets ISO 26262, IEC 61508

Enhanced SoC Safety

Hardware-centric safety and data protection

Simplified Architecture

Reduced complexity versus software approaches

High-Quality Assurance

Pre-tested hardware IP ensures reliability

Adaptable Data Protection

Support for leading processors & ECC features

Inherent Redundancy

Unit duplication for fault-tolerance

Versatile Applications

Ideal for automotive, SSD controllers, & more

Optimized Control

Baseline safety features, reducing risk

Read more about why we are unique on our NoC Technology page.