What is a NoC Interconnect?

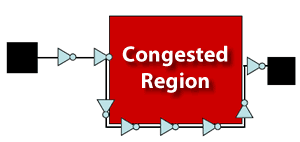

Network-on-chip (NoC) interconnect technology is often called “a front-end solution to a back-end problem.” As semiconductor transistor dimensions shrink and increasing amounts of IP block functions are added to a chip, the physical infrastructure that carries data on the chip and guarantees quality of service begins to crumble. Many of today’s systems-on-chip are too complex to utilize a traditional hierarchal bus or crossbar interconnect approach. Yesterday’s village traffic has turned into today’s congested freeways.

Here are four reasons why today’s SoC’s need a NoC interconnect fabric:

Reduce Wire Routing Congestion

Arteris’ NoC interconnect fabric technology significantly reduces the number of wires required to route data in a SoC, reducing routing congestion at the backend of the design process. Backend wire routing congestion has become one of the most significant factors causing late designs as the number of IP blocks on a SoC has increased.

Ease Timing Closure

The distributed architecture of Arteris network on chip interconnect fabrics allows for precise placement of pipelines (aka “register slices”) to easily resolve timing closure issues without affecting other areas of the chip.

The distributed architecture of Arteris network on chip interconnect fabrics allows for precise placement of pipelines (aka “register slices”) to easily resolve timing closure issues without affecting other areas of the chip.

Higher Operating Frequencies

NoC interconnects simplifies the hardware required for switching and routing functions, allowing SoCs with NoC interconnect fabrics to reach higher operating frequencies.

Furthermore, for long or speed-sensitive paths, the architect can easily place pipeline registers along any connection, allowing for higher frequencies. Precise placement of pipeline registers (also called “register slices”) allows the interconnect to exactly accommodate the SoC’s timing budget and meet its target frequency, with less pipeline register latency and no effect on neighboring IP block timing.

In addition to pipelining, distributed globally asynchronous locally synchronous (GALS) technology allows synchronous modules with locally generated clocks, with asynchronous connections between them.

In short, NoC technology’s simpler switching and routing hardware, fine granularity pipelining capability, and GALS allow NoC interconnects to achieve higher operating frequencies than inferior multi-layered bus or crossbar interconnects.

Easy Derivative Chips: Change IP Easily

Arteris NoC technology makes it easy to swap IP blocks to create derivative chips or to respond quickly to engineering change orders (ECOs) during development because Arteris NoC interconnects are protocol agnostic. In an Arteris NoC interconnect fabric, the transaction (protocol) layers are separate from the transport and physical layers. Small network interface units (NIUs) that convert IP protocol transaction into transport packets are synthesized close to initiator and target IP blocks, allowing the rest of the interconnect topology to be made of simpler IP blocks that perform switching and routing.

Arteris’ network-on-chip interconnect IP allows us to reduce the die size of Mobileye’s 3rd generation vision processor, EyeQ3, optimize latency for critical IP blocks and reach timing closure much sooner than expected.

Elchanan Rushinek, Vice President of Engineering, Mobileye