Connected by Arteris: Navigating Integration Challenges for the RISC-V Ecosystem with Networks-on-Chips (NoCs)

by On Mar 07, 2024

In the rapidly evolving landscape of semiconductor developments for advanced applications for the consumer, mobile, communications, industrial, and automotive verticals, RISC-V stands out as an emerging alternative processor instruction set architecture (ISA) promising innovation and flexibility. RISC-V’s promise of “Freedom to Innovate” also comes with great responsibility in the verification and validation of the processor architectures itself. Most of the related innovation happens in the area of the ISA itself. Still, inadvertently, experts in the RISC-V community must understand the multifaceted challenges and opportunities the challenge of system-on-chip (SoC) integration that come with adopting this open-standard architecture.

Arteris is known as the pioneer of Network-on-Chip (NoC) development, and you can find us when writing this Blog in more than 3.5 billion SoCs shipped. Our commitment has always been to support any processor, multiple NoC protocols for SoC integration, and deliver productivity to our users with flexible configuration of NoC topologies. We recognize the transformative potential of RISC-V and are committed to guiding you through the complexities of SoC design, focusing on Networks on Chip (NoC) and the emerging field of chiplets.

Let’s dive into it.

The Customization Conundrum

One of the most compelling attributes of RISC-V is its flexibility, allowing designers to tailor architectures to specific needs. However, this customization brings about significant SoC integration challenges. Each RISC-V integration is unique, requiring a custom approach to align all the semiconductor IP components – whether reused or developed from scratch for differentiation – considering their various interfaces and protocols. Ensuring seamless communication between heterogeneous elements within an SoC requires understanding the “language” they speak. I previously discussed the complexity of specific protocols like AMBA AXI, APB, ACE, CHI, OCP, CXL, and others in “Design Complexity In The Golden Age Of Semiconductors.” One must read several thousand pages of documentation to understand the options here.

Navigating Cache Coherency and Throughput Predictability

Cache coherency and throughput predictability are critical for computing applications, especially as performance requirements and data sharing for computing engines grow. Integrating RISC-V cores into SoCs demands very detailed planning to achieve optimal performance. The variability in latency and throughput inherent in custom solutions requires a clear understanding of cache coherency mechanisms and memory management strategies. These challenges underscore the need for advanced NoC development solutions to adeptly manage data flow and ensure consistent performance across diverse computing environments. In “NoC Development – Make Or Buy?” I recently looked at the intricacies and development efforts of developing a NoC from scratch. Calling Arteris and talking to us, the experts, is a clear alternative 😉

The Role of Network on Chip (NoC)

In addressing the complexities of SoC integration, NoCs emerge as a critical component. They are used to manage design complexity to guide divide and conquer during the development process, connecting subsystems and the top-level of advanced SoCs. In modern SoCs, we often see 10s of NoCs connecting 100s initiators and targets across the SoC.

Arteris’ NoC technology facilitates the efficient management of data traffic within SoCs, offering a scalable solution to the challenges posed by heterogeneous integration. By enabling predictable latency and supporting diverse communication protocols, NoC architectures play a pivotal role in successfully deploying RISC-V-based SoCs. They provide a flexible framework that adapts to the specific requirements of each integration, from simple designs to complex multicore systems. As

The Emergence of Chiplets and The Future of Heterogeneous Computing

The rise of RISC-V inextricably links to the broader trend towards heterogeneous computing. As systems incorporate a more comprehensive array of specialized processors and accelerators, the integration challenges become more pronounced. Efficiently managing communication and data sharing across diverse components is critical.

The shift towards chiplet-based designs represents a significant evolution in the semiconductor industry, offering a pathway to greater modularity, cost efficiency for designs that exceed the reticle limit, and product portfolio management. I wrote more about this recently in “Watching The Next Big Semiconductor Transition Unfold” when looking at the most recent Chiplet Summit. Integrating RISC-V cores within a chiplet architecture presents unique challenges, particularly regarding interoperability and interface standardization. The coordination between chiplets, each potentially housing different RISC-V configurations, necessitates a comprehensive integration approach considering physical, thermal, and electrical interactions. Expertise in NoC technologies becomes increasingly critical in this context, providing the tools and knowledge to streamline chiplet integration and maximize system performance.

Architectural Decisions and Ecosystem Considerations

The adoption of RISC-V and the integration of SoCs involve critical decisions at the architectural level. Developers must navigate the trade-offs between performance, power consumption, and area efficiency while considering the long-term implications of their design choices. An in-depth understanding of the RISC-V ecosystem, including available tools, libraries, and debug capabilities, is essential for successful integration. With our partners in the architecture exploration space – like Synopsys and their Platform Architect offering to which our tools seamlessly interface – we are committed to supporting the RISC-V community through this journey, offering insights and solutions that address these complex considerations.

Addressing Physical Challenges

Beyond the logical integration of SoCs, physical factors such as power distribution, signal integrity, and thermal management play a crucial role in the success of RISC-V-based designs. As chips become more complex and power-hungry, ensuring efficient heat dissipation and maintaining signal integrity across the SoC becomes increasingly challenging. Efficient NoC implementations are critical in mitigating these physical effects, enabling more reliable and efficient systems. I have discussed this aspect and the architecture considerations in length in the past, for instance, in “The Architect’s Dilemma And Closing The Loop With Implementation” and “Shortening Network-On-Chip Development Schedules Using Physical Awareness.”

Connecting, Unifying, and Derisking NoC Development for the RISC-V Ecosystem

The journey towards integrating RISC-V into SoCs is fraught with challenges but also ripe with opportunity. By understanding and addressing the complexities of SoC design, cache coherency, throughput predictability, and the role of NoC, developers can unlock the full potential of RISC-V. The advent of chiplets further expands the design landscape, offering new ways to enhance modularity and reduce costs.

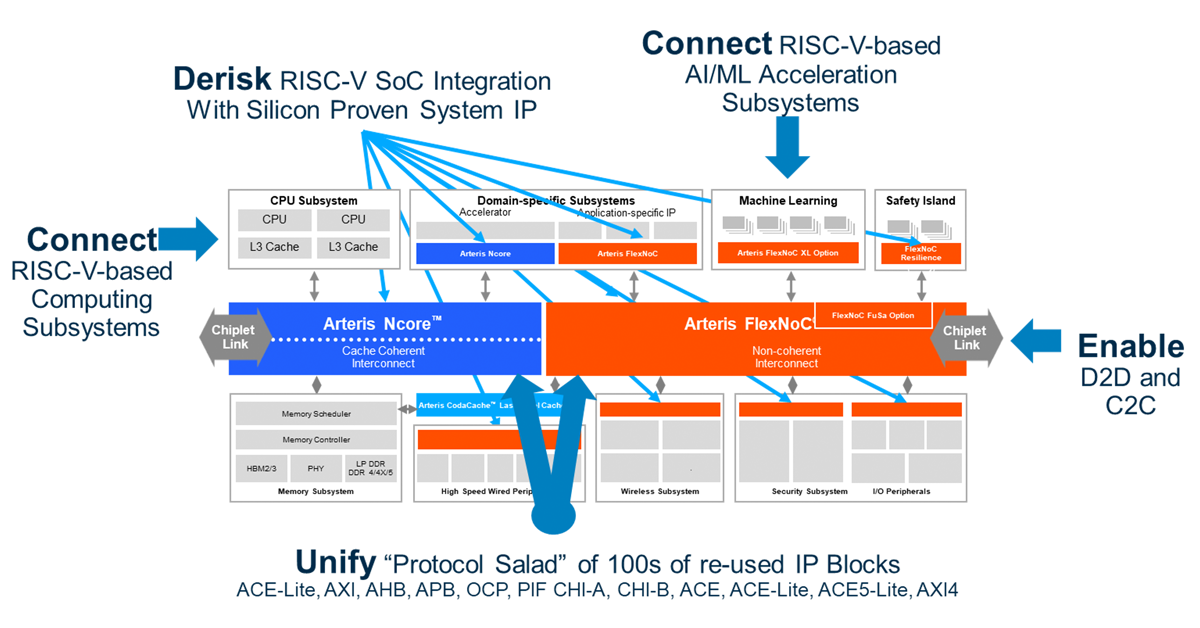

When looking at typical SoC architectures such as the one below, NoC development frameworks can help the RISC-V community to unify the NoC protocol salad they face when integrating RISC-V IP blocks with 100s of other reused blocks with potentially different protocol variants. They help connect different types of SoC subsystems while considering the intricate protocol aspects of die-to-die and chip-to-chip connections. Combined, they help derisk SoC development as developers can focus on differentiation with their RISC-V customization – using RISC-V’s promise of “Freedom to Innovate” while relying on silicon-proven IP for the NoCs.

As we navigate these challenges together, Arteris remains a steadfast partner to the RISC-V community, providing the tools, knowledge, and support needed to usher in a new era of processor development. Together, we can drive innovation, optimize performance, and democratize chip design, leveraging the power of RISC-V to shape the future of technology.